Verilog My16ChannelCounter

- Date:

11 Oct 2019

What is the idea?

The following is just a simple counter

So it counts signals from 16 channels, each with 32 bits, then group them to 512 bits as output

Other than the 16 bits input, we also have eight 16 bits inputs, these are masks to group certain channels together. Of course, you will also find the corresponding eight outputs

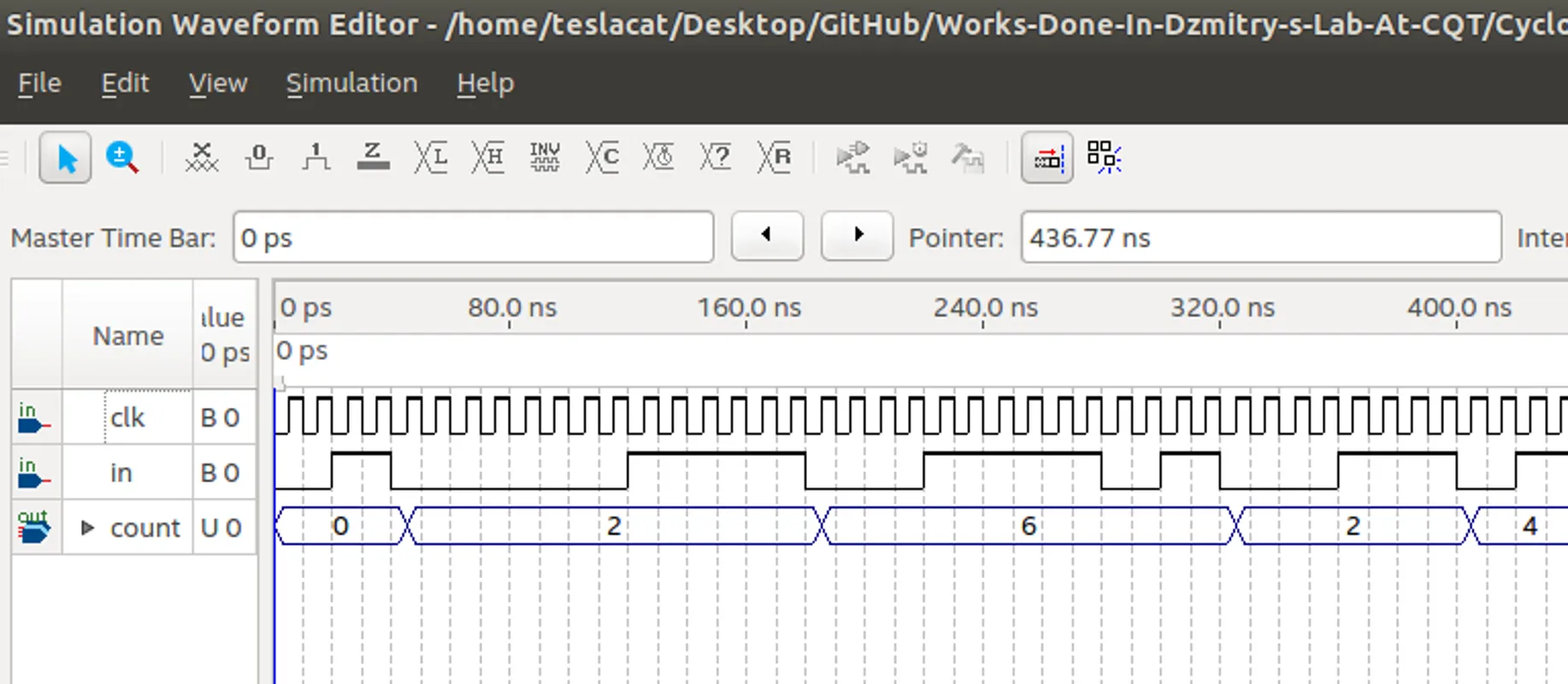

Simple Counter Submodule

module Counter(

input clk,

input in,

output reg [31:0] count

);

// Begin internal signals

reg [31:0] cnt;

reg lastIn;

// End internal signals

// Begin count

always @(posedge clk) begin

if(in) begin

cnt <= cnt +1;

end

else if(lastIn==1 && in==0) begin

count <= cnt;

cnt <= 0;

end

lastIn<=in;

end

// End count

endmodule

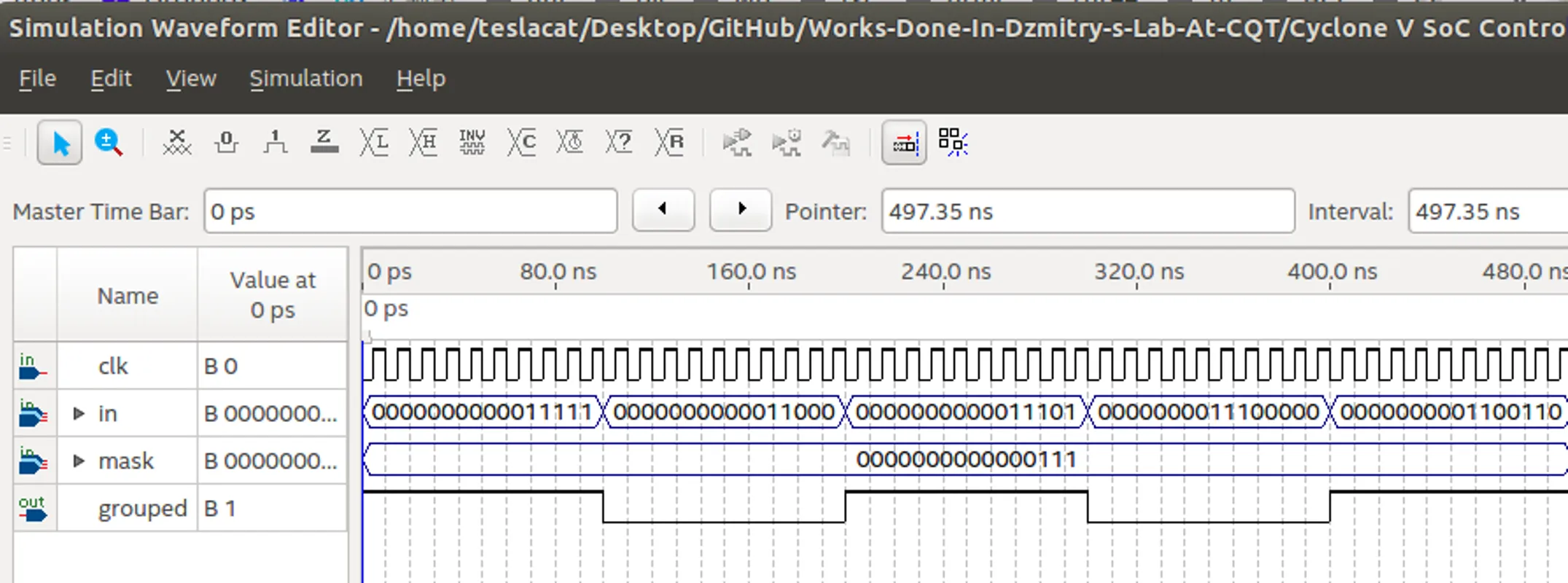

Simple Grouper Submodule

module Grouper(

input [15:0] mask,

input [15:0] in,

output grouped

);

assign grouped = (mask & in) ? 1:0;

endmodule

I know you might wonder why I have to create a one line module

Trust me, when you do big projects, coding style is very important!

Main Module

module My16ChannelCounter(

input clk,

// counters

input [15:0] in16Channels,

output [511:0] zippedCount,

// groupers

input [15:0] mask0,

input [15:0] mask1,

input [15:0] mask2,

input [15:0] mask3,

input [15:0] mask4,

input [15:0] mask5,

input [15:0] mask6,

input [15:0] mask7,

output [7:0] grouped

);

// Begin internal signals

// for Counter

wire [31:0] wire_count0,wire_count1,wire_count2,wire_count3;

wire [31:0] wire_count4,wire_count5,wire_count6,wire_count7;

wire [31:0] wire_count8,wire_count9,wire_count10,wire_count11;

wire [31:0] wire_count12,wire_count13,wire_count14,wire_count15;

// for Grouper

wire wire_grouped0,wire_grouped1,wire_grouped2,wire_grouped3;

wire wire_grouped4,wire_grouped5,wire_grouped6,wire_grouped7;

// End internal signals

// Begin Counter

Counter channel0(.clk(clk),.in(in16Channels[0]),.count(wire_count0));

Counter channel1(.clk(clk),.in(in16Channels[1]),.count(wire_count1));

Counter channel2(.clk(clk),.in(in16Channels[2]),.count(wire_count2));

Counter channel3(.clk(clk),.in(in16Channels[3]),.count(wire_count3));

Counter channel4(.clk(clk),.in(in16Channels[4]),.count(wire_count4));

Counter channel5(.clk(clk),.in(in16Channels[5]),.count(wire_count5));

Counter channel6(.clk(clk),.in(in16Channels[6]),.count(wire_count6));

Counter channel7(.clk(clk),.in(in16Channels[7]),.count(wire_count7));

Counter channel8(.clk(clk),.in(in16Channels[8]),.count(wire_count8));

Counter channel9(.clk(clk),.in(in16Channels[9]),.count(wire_count9));

Counter channel10(.clk(clk),.in(in16Channels[10]),.count(wire_count10));

Counter channel11(.clk(clk),.in(in16Channels[11]),.count(wire_count11));

Counter channel12(.clk(clk),.in(in16Channels[12]),.count(wire_count12));

Counter channel13(.clk(clk),.in(in16Channels[13]),.count(wire_count13));

Counter channel14(.clk(clk),.in(in16Channels[14]),.count(wire_count14));

Counter channel15(.clk(clk),.in(in16Channels[15]),.count(wire_count15));

assign zippedCount = {

wire_count15,wire_count14,wire_count13,wire_count12,

wire_count11,wire_count10,wire_count9,wire_count8,

wire_count7,wire_count6,wire_count5,wire_count4,

wire_count3,wire_count2,wire_count1,wire_count0

};

// End Counter

// Begin Grouper

Grouper group0(.mask(mask0),.in(in16Channels),.grouped(wire_grouped0));

Grouper group1(.mask(mask1),.in(in16Channels),.grouped(wire_grouped1));

Grouper group2(.mask(mask2),.in(in16Channels),.grouped(wire_grouped2));

Grouper group3(.mask(mask3),.in(in16Channels),.grouped(wire_grouped3));

Grouper group4(.mask(mask4),.in(in16Channels),.grouped(wire_grouped4));

Grouper group5(.mask(mask5),.in(in16Channels),.grouped(wire_grouped5));

Grouper group6(.mask(mask6),.in(in16Channels),.grouped(wire_grouped6));

Grouper group7(.mask(mask7),.in(in16Channels),.grouped(wire_grouped7));

assign grouped = {

wire_grouped0,wire_grouped1,wire_grouped2,wire_grouped3,

wire_grouped4,wire_grouped5,wire_grouped6,wire_grouped7

};

// End Grouper

endmodule